set_clock_transition в VLSI | Полное объяснение команды SDC для начинающих STA

Автор: Maharshi Sanand Yadav T

Загружено: 2025-11-04

Просмотров: 1

Характеристика стандартной ячейки = • standard cell characterization

STA = • STA || Static Timing Analysis

Синтез и STA = • Synthesis and STA

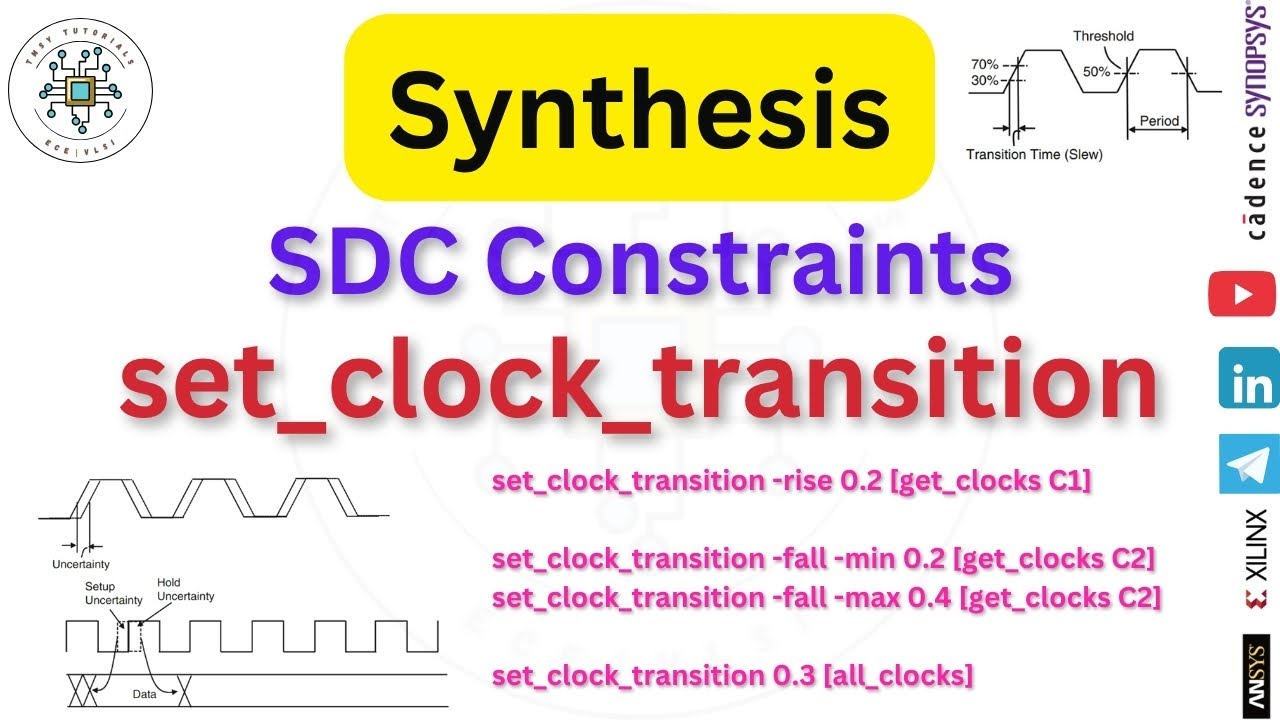

В этом видео мы объясним команду SDC set_clock_transition — одно из важнейших временных ограничений, используемых в статическом временном анализе (STA) и синтезе. Независимо от того, являетесь ли вы новичком в разработке СБИС, инженером STA или стажёром по физическому проектированию, это руководство поможет вам чётко понять, как и почему мы используем set_clock_transition в файлах ограничений проектирования.

🧠 Что вы узнаете из этого видео:

Что такое переход тактового сигнала (или нарастание тактового сигнала) в СБИС

Зачем set_clock_transition нужен в STA

Синтаксис и использование команды set_clock_transition

Как определить значения нарастания и спада тактового сигнала

Как эта команда влияет на анализ установки и удержания

Практические примеры с Cadence Genus и Synopsys Design Compiler

Разница между set_clock_transition и set_input_transition

Часто задаваемые вопросы на собеседовании, связанные с переходом тактового сигнала

💡 Почему это важно:

Переход тактового сигнала (или нарастание тактового сигнала) определяет скорость изменения тактового сигнала с логического 0 на 1 и наоборот. Неправильно определённый или нереалистичный нарастание тактового сигнала может привести к неточным расчётам задержки и синхронизации во время синтеза и STA. Применяя set_clock_transition, вы гарантируете, что временной анализ соответствует реальным условиям, а сети синхронизации разработаны для оптимальной производительности.

set_clock_transition -rise 0.05 -fall 0.05 [get_clocks clk]

🧩 Рассматриваемые темы:

Определение изменения тактовой частоты

Влияние перехода на время установки/удержания

Синтаксис SDC и примеры

Как инструменты EDA интерпретируют значения перехода тактовой частоты

Влияние на отчёты о времени и оптимизацию

✨ Оставайтесь на связи со мной:

🔗 LinkedIn: / t-maharshi-sanand-yadav

🔗 Instagram: / vlsi.tmsy.tutorials

🎓 Ознакомьтесь с моим курсом на Udemy:

🔗 Проектирование цифровых систем с использованием Verilog HDL: https://www.udemy.com/course/digital-...

✨ Хэштеги для охват:

#tmsytutorials #tmaharshisanandyadav #статическийанализвремени #sta #DTA #vlsi #vlsitraining #chipdesign #синтез #физическоепроектирование #PrimeTime #tempus #redhawk #STAtools #DTAtools #STAinVLSI #DTAinVLSI #TimingAnalysis #timingclosure #VLSITutorials #VLSILearning #VLSIInterviewQuestions #VLSICourse #vlsijobs #asic #fpga #vlsidesign #rtldesign #RTLtoGDSII #цифровоепроектирование #Voltus #cadence #synopsys #ansys #компиляторпроектирования #genus #Innovus #edatools #socdesign #проверкачипирования #статическийанализ #динамическийанализ #проверкавремени #STAflow #STAprocess #отчётыповремени #расчётзадержки #времяустановки #времяудержания #clocktreesynthesis #cts #signalintegrity #PowerAnalysis #IRDrop #EMAnalysis #NoiseAnalysis #GateLevelSimulation #PostLayoutSimulation #FunctionalVerification #RTLVerification #TimingSignoff #SignoffTools #STAengineer #DTAengineer #BackendDesign #frontenddesign #ChipImplementation #asicdesign #FPGAprototyping #icdesign #semiconductors #SiliconDesign #vlsiprojects #VLSIResearch #StandardCells #LibraryCharacterization #eda #hardwaredesign #logicdesign #circuitdesign #digitalelectronics #edasoftware #ChipTapeout #VLSILab #VLSItools #NetlistAnalysis #SDF #LibFiles #SDFAnnotation #TimingLib #TimingClosureFlow #designflow #RTL2GDS #EDAflow #SemiconductorEngineering #SoCtiming #AdvancedNodes #TimingOptimization #ClockDomainCrossing #VLSItips

Доступные форматы для скачивания:

Скачать видео mp4

-

Информация по загрузке: