ARM ISA Overview | ARM Architecture, Registers, Addressing Modes & Instructions

Автор: E&C SIMPLIFIED

Загружено: 2025-10-20

Просмотров: 36

Understand the ARM ISA (Instruction Set Architecture) in this clear and beginner-friendly video. We break down the core concepts behind ARM architecture, including its register sets, instruction types, addressing modes, and architecture versions like ARMv7, ARMv8, and ARMv9.

Whether you're a student, engineer, or tech enthusiast, this video will give you a solid foundation in how ARM-based CPUs work and why they dominate embedded systems, smartphones, and IoT devices.

🔹 Topics Covered:

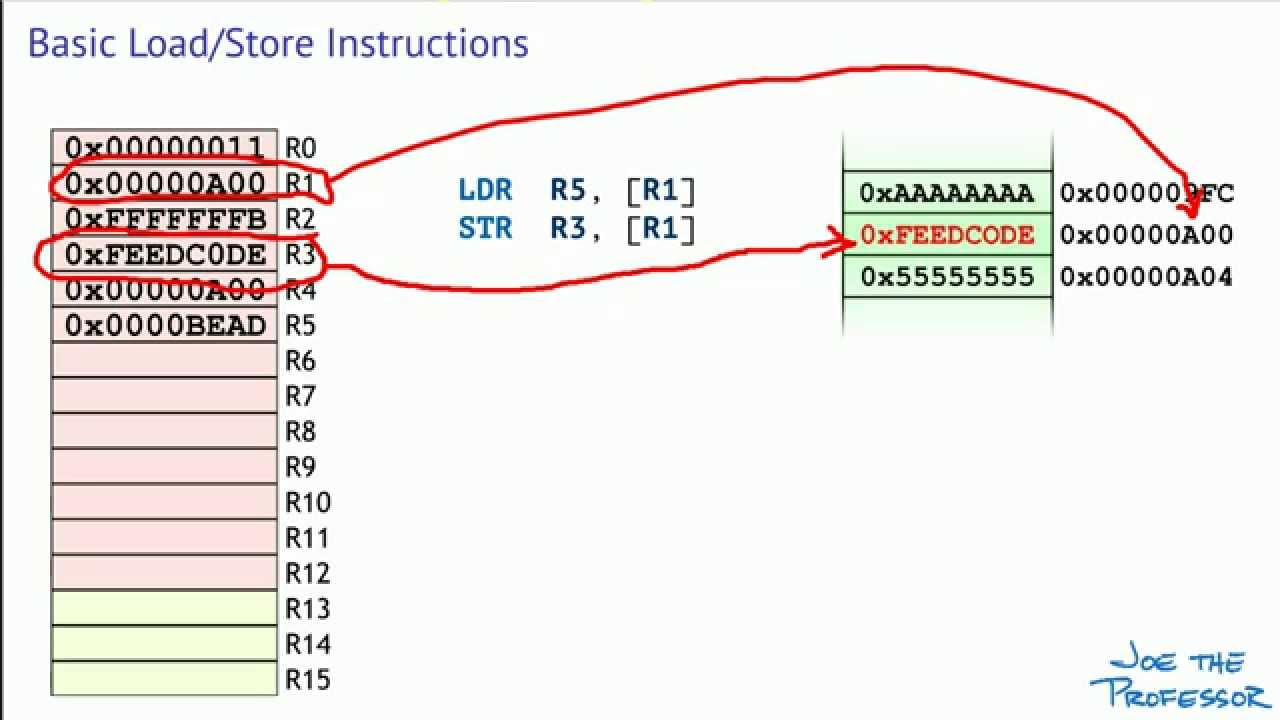

• ARM register sets: general-purpose, special-purpose, and status registers

• Common addressing modes in ARM (immediate, register, PC-relative, etc.)

• Instruction types: data processing, load/store, branch

• RISC principles in ARM

• ARM architecture versions: ARMv7, ARMv8, ARMv9

📘 Ideal for:

Computer science students

Embedded systems engineers

Anyone learning ARM assembly or low-level programming

👍 Like the video, subscribe for more content on computer architecture, and drop a comment with your questions!

#ARM #ComputerArchitecture #EmbeddedSystems #AssemblyProgramming #ARMISA #TechExplained

Доступные форматы для скачивания:

Скачать видео mp4

-

Информация по загрузке: