Design of Latches and Flip-Flops using CMOS Circuits | VLSI Design Tutorial

Автор: VLSI Simplified

Загружено: 2025-10-16

Просмотров: 84

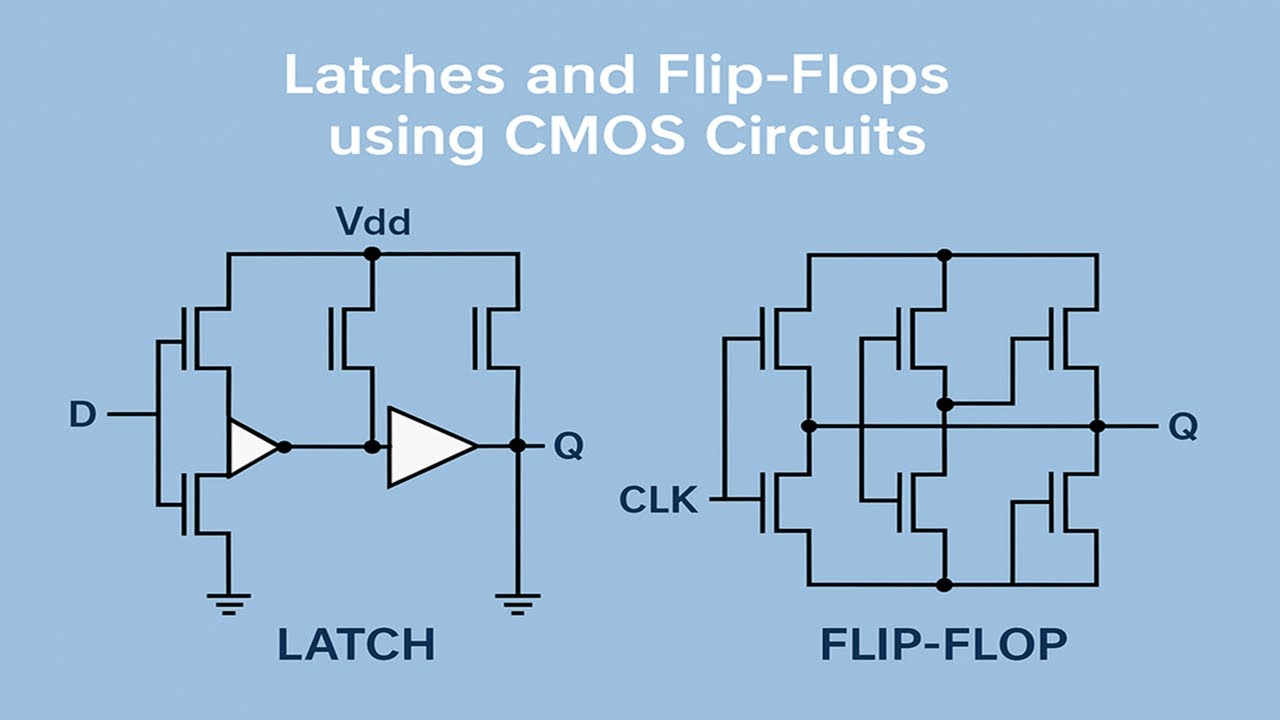

In this video, we explore the design and working of Latches and Flip-Flops using CMOS technology. Learn how basic memory elements are built from transistor-level circuits, and understand their operation, timing behavior, and logic functionality in detail.

🔍 Topics Covered:

Introduction to Sequential Circuits

SR Latch, D Latch, and JK Flip-Flop using CMOS logic

Transmission gates and clocking concepts

Comparison between Latches and Flip-Flops

Design considerations and transistor-level analysis

Simulation insights for CMOS-based sequential elements

This session is ideal for VLSI learners, students, and engineers who want to strengthen their understanding of sequential circuit design at the transistor level.

💻 Subscribe for more tutorials on VLSI Design & Verification!

🔔 Stay tuned for upcoming videos on CMOS Design, RTL Implementation, and Testbench Development.

📘 Tags:

#CMOSDesign #Latches #FlipFlops #VLSI #SequentialCircuits #SRLatch #DFlipFlop #TransmissionGate #ASICDesign #SystemVerilog #RTLDesign #VLSITraining #GnanodayaVLSI #DigitalElectronics

Доступные форматы для скачивания:

Скачать видео mp4

-

Информация по загрузке: