Phase Locked Loop - basic principle - Digital PLL

Автор: Computer&Electronics

Загружено: 31 июл. 2024 г.

Просмотров: 4 256 просмотров

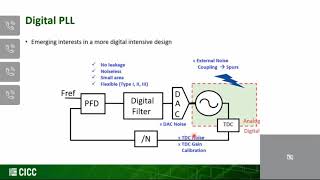

A phase locked loop is a device which generates a clock and sychronizes it with an input signal. The input signal can be data or another clock. A very common application is frequency synthesis. In frequency synthesis PLLs are used to generate a clock which is based on a clock already existing. Often the newly generated clock will be at a multiple of the original frequency and this is what the video is about: generating a clock that is a multiple of a reference clock.

D Flip Flop • D Flip Flop and frequency divider

Current Mirror : • BJT Current Mirror Basic Principle

uA741 Operational Amplifier: • ua741 Operational Amplifier - Op-Amp inter...

Material taken from the book “CMOS, Circuit design, layout and simulation” by J Baker, H. H. Li, D. E. Boyce

Доступные форматы для скачивания:

Скачать видео mp4

-

Информация по загрузке: