Digital logic #8: Circuit minimization: Boolean Algebra, Karnaugh maps, & Quine–McCluskey algorithm

Автор: Aaron Dahlen

Загружено: 2021-02-24

Просмотров: 1484

Summary:

This video develops methods for minimizing combinational logic starting from sum-of-products and sums of minterms. Worked examples show how Karnaugh maps and the Quine–McCluskey algorithm generate equivalent optimized expressions. The instructor also compares resulting gate counts to highlight hardware savings.

Why This Matters:

Logic minimization directly affects hardware cost, power, and required gate fan-in in real designs. Understanding both graphical and tabular methods prepares you for larger input spaces and automation. These skills transfer to FPGA mapping, PLA design, and digital optimization courses.

Content covered in the video:

Distinguishing sum of products versus sums of minterms, and expanding an SOP expression into a compact sum of minterms.

Relating adjacency of minterms to single-bit changes in binary encoding and using that structure for simplification.

Constructing 3- and 4-variable Karnaugh maps, labeling cells by minterm index, and placing function values.

Grouping 1s into valid implicants, translating groups into product terms, and checking for larger overlapping groupings.

Comparing hardware realizations: naïve four-input AND implementations for each minterm versus minimized three-input structures.

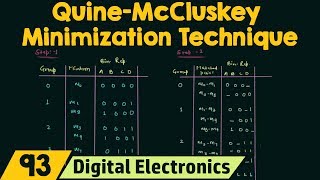

Step-by-step Quine–McCluskey procedure, including grouping by ones count, forming pairs, propagating x positions, and tracking uncovered minterms.

Practical limits of Karnaugh maps as input count grows, and motivation for algorithmic minimization and eventual software automation.

Доступные форматы для скачивания:

Скачать видео mp4

-

Информация по загрузке: